Sean Riley介绍说,Lattice ECP4提供多达250K LUT的逻辑密度和10.6Mbit存储器以便于系统集成、可级联的高性能DSP模块用于信号处理、高速存储器接口,包括1066Mbps的DDR3以及高达1.25Gbps的LVDS性能,适用于ADC/DAC,并且实现了高速串行I/O。此外,Lattice ECP4还提供经验证的6Gbps低功耗SERDES,可构建高速系统,6Gbps低功耗SERDES是专为支持各种协议而设计的,例如,PCI Express 2.1、以太网(10GbE、GbE、SGMII、XAUI & RXAUI)、串行RapidIO 2.1和低延迟CPRI。为了加快采用Lattice ECP4的系统设计,Lattice将提供大量通用和特定应用的开发套件、一系列扩展的免费参考设计以及经济的IP套件。

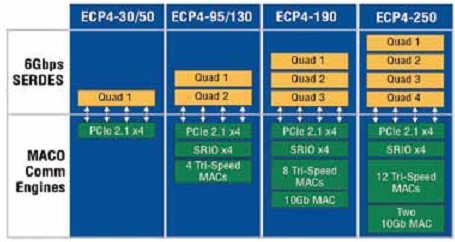

Lattice ECP4 FPGA SERDES和MACO通信引擎。

Sean Riley告诉记者,Lattice ECP4还是使用成熟的低成本的65nm工艺 ,采用广泛使用的wire-bond封装。和ECP3相比,Lattice ECP4的优势还体现在:一是ECP4包含多达16个符合CEI标准的6Gbps SERDES通道,具有嵌入式物理编码子层(PCS)模块,在6G下工作每通道功耗低于175mW,使客户能够选择以芯片到芯片以及远距离背板应用的方式部署ECP4,MACO通信引擎可为通用通信协议节省10倍的功耗和资源;二是ECP4系列具有功能强大的数字信号处理(DSP)模块,独特的加速逻辑意味着每个ECP4 DSP模块,4倍于上一代ECP3器件的信号处理能力;三是ECP4的速度比上一代器件快50%,具有1066Mbps的DDR3存储器接口和1.25Gbps的LVDS I/O,也可作为串行千兆以太网接口。新的LatticeECP4 系列还有66%以上的逻辑资源和42%以上的嵌入式存储器,使设计工程师能够在FPGA中构造完整的片上系统。

据了解,目前已有客户在使用Lattice Diamond 1.4 beta设计软件用Lattice ECP4 FPGA进行设计。在2012年的上半年可获取器件样品,预计2012年下半年大批量生产并发货。(丛秋波)