晶体管越来越小,芯片也越来越快,但无论芯片有多快,将数据从一边移动到另一边仍然需要时间。到目前为止,芯片设计师是通过放置充当缓存的本地存储器解决 这个问题。

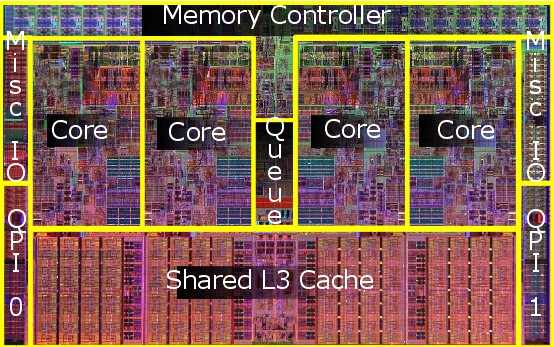

缓存被用于储存最频繁访问的数据,便于访问。但让一个缓存服务于一个处理器或一个核心的时代已经过去,缓存的管理变成了一大挑战,而处理器核心 之间需要共享数据,连接核心的通信网络的物理布局也必须考虑在内。

现在,MIT和康涅狄克大学的研究人员为多核芯片设计了一套新的缓存管理规则,能显著改进芯片性能,降低能耗。论文《The Locality-Aware Adaptive Cache Coherence Protocol(PDF)》发表在IEEE International Symposium on Computer Architecture会议上,新缓存设计减少芯片15%的执行时间,节省25%的能耗。